技術情報 半導体デバイスEMC試験

半導体デバイスのEMC試験規格には、主にイミュニティ試験法を規定したIEC 62132シリーズとエミッション測定を規定したIEC 61967シリーズがあります。近年、JEITAやJASO規格では半導体EMC性能等価性評価を規定する際の試験方法としてイミュニティ試験ではDPI法、エミッション測定では1Ω/150Ω法が採用されました。

この背景には、大半の試験方法がIC全体に対してノイズを印加または測定する方式に対して、DPI法および1Ω/150Ω法は、ICの個々のピンに対してノイズの評価が行える試験方法となり、詳細な差異確認ができるメリットがあるためです。

上記理由に伴い、現在の半導体デバイスのEMC試験規格では、イミュニティ試験はIEC 62132-4で規定されているDPI法、エミッション測定はIEC 61967-4で規定されている1Ω/150Ω法が主流の試験方法となっています。

| 項目 | 規格番号 | 対象 | 測定方法 |

|---|---|---|---|

| イミュニティ試験 EMS | IEC 62132-1 | 【一般条件と定義】General conditions and definitions | |

| IEC 62132-2 | 放射ノイズ | 【TEMセル法】TEM cell and wideband TEM cell method | |

| IEC 62132-3 | 伝導ノイズ | 【BCI法】BCI(Bulk Current Injection)method | |

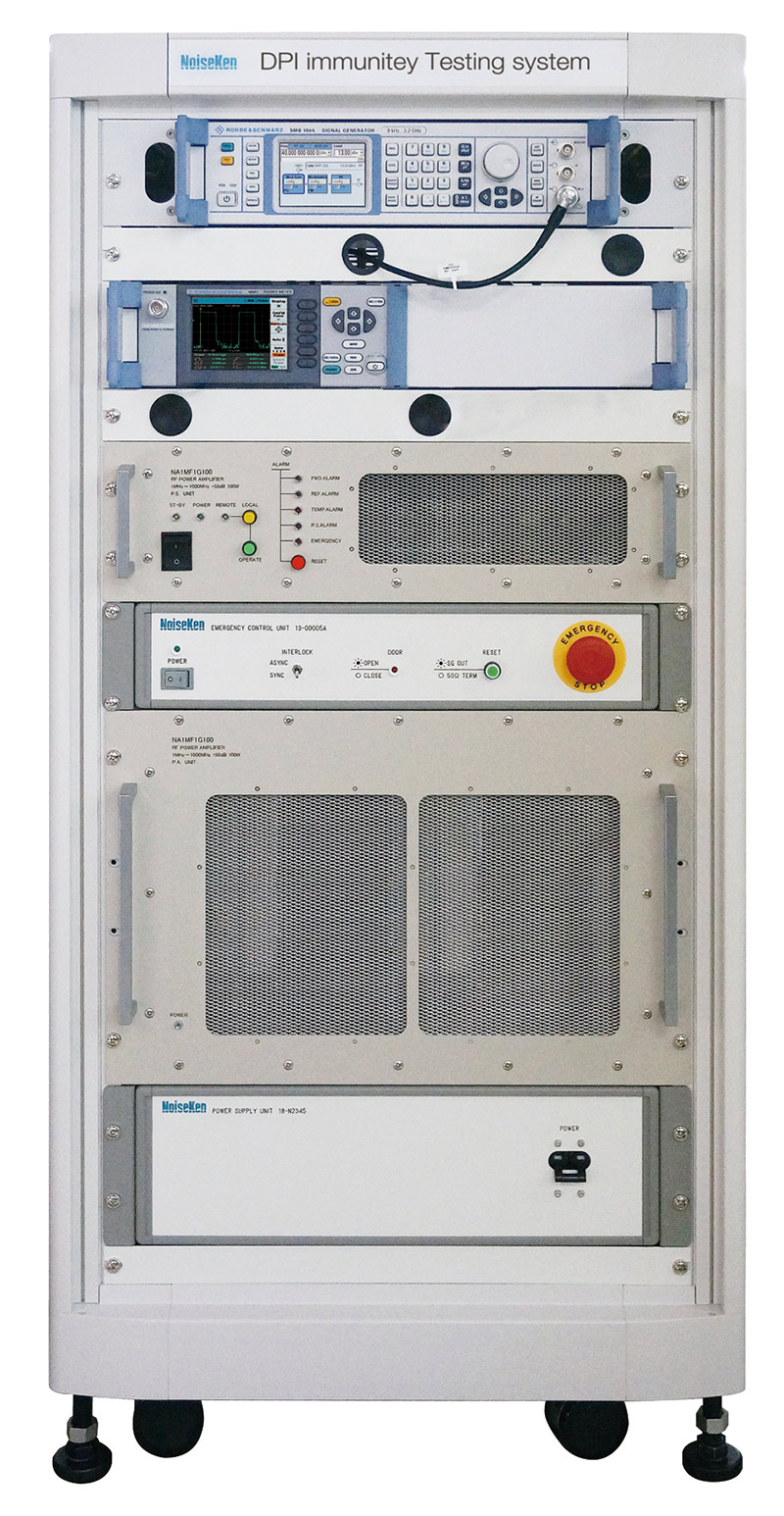

| IEC 62132-4 | 伝導ノイズ | 【DPI法】DPI(Direct RF power Injection)method | |

| IEC 62132-5 | 伝導ノイズ | 【WBFC法】WBFC(Workbench Faraday Cage)method | |

| IEC 62132-8 | 放射ノイズ | 【ICストリップライン法】IC stripline method | |

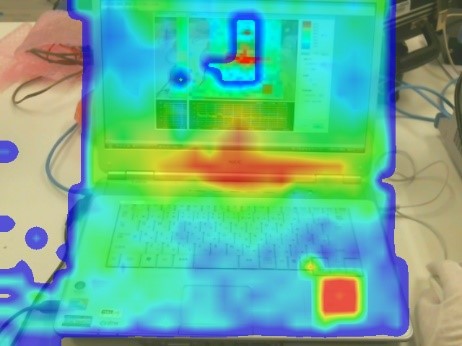

| IEC 62132-9 | 放射ノイズ | 【表面走査法】Surface scan method | |

| エミッション測定 EMI | IEC 61967-1 | 伝導ノイズ | 【一般条件と定義】General conditions and definitions |

| IEC 61967-2 | 放射ノイズ | 【TEMセル法】TEM cell and wideband TEM cell method | |

| IEC 61967-3 | 放射ノイズ | 【表面走査法】Surface scan method | |

| IEC 61967-4 | 伝導ノイズ | 【1Ω/150Ω法】1Ω/150Ω direct coupling method | |

| IEC 61967-5 | 伝導ノイズ | 【WBFC法】WBFC(Workbench Faraday Cage)method | |

| IEC 61967-6 | 伝導ノイズ | 【MP法】Magnetic probe method | |

| IEC 61967-8 | 放射ノイズ | 【ICストリップライン法】IC stripline method |

放射ノイズは空間を伝わるノイズの評価方法。伝導ノイズはケーブルなどに伝わるノイズの評価方法。各規格の詳細な測定方法等につきましては規格書の原文をご参照下さい。

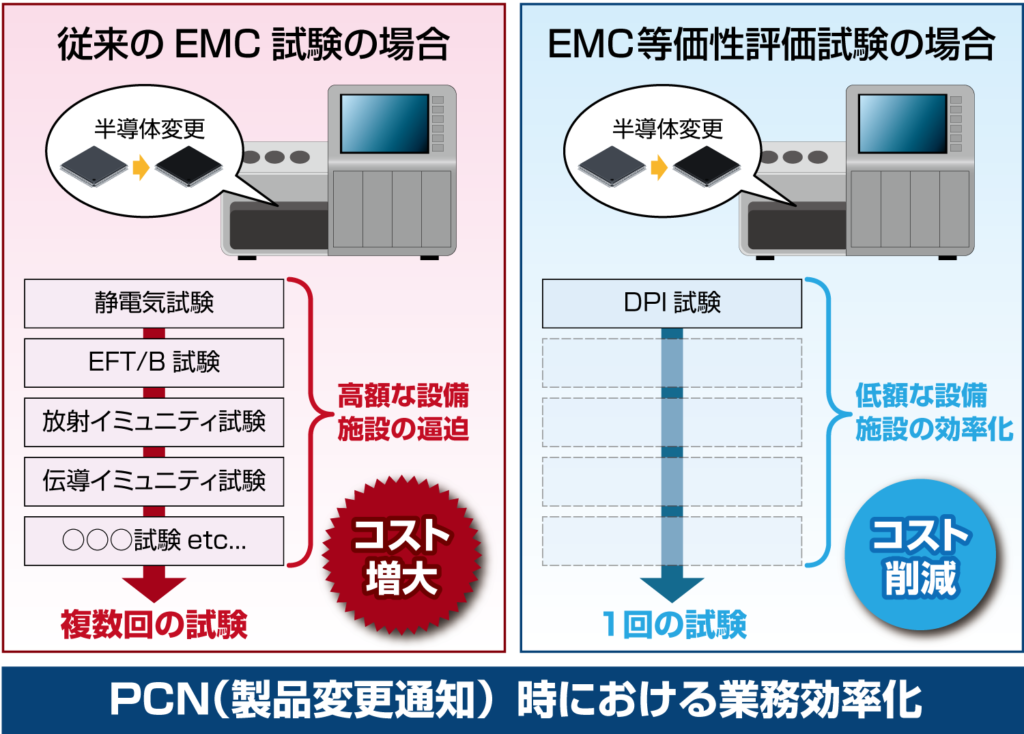

【半導体EMC性能等価性評価による試験工数削減 】

半導体EMC性能等価性評価は機能が同一であり、端子構成及び端子位置に変更がなく、かつ電気的特性に差異がない製品間に対して行います。評価法は電子情報技術産業協会よりJEITA ED-5008(半導体EMC性能等価性評価法)が2020年7月に、自動車技術会からはJASO D 019(自動車用半導体EMC性能等価性試験法)が2021年3月に制定されました。

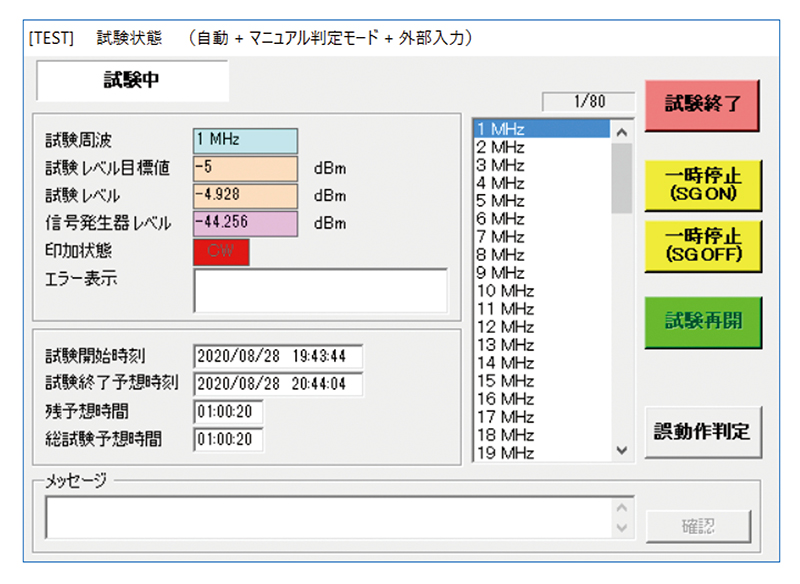

評価は伝導イミュニティ性能等価評価および伝導エミッション性能等価評価の2つがありますが、伝導イミュニティ性能等価評価はDPI法で行い、変更する半導体製品(IC)の等価性の証明ができれば、製品性能は同等と見なすことができます。

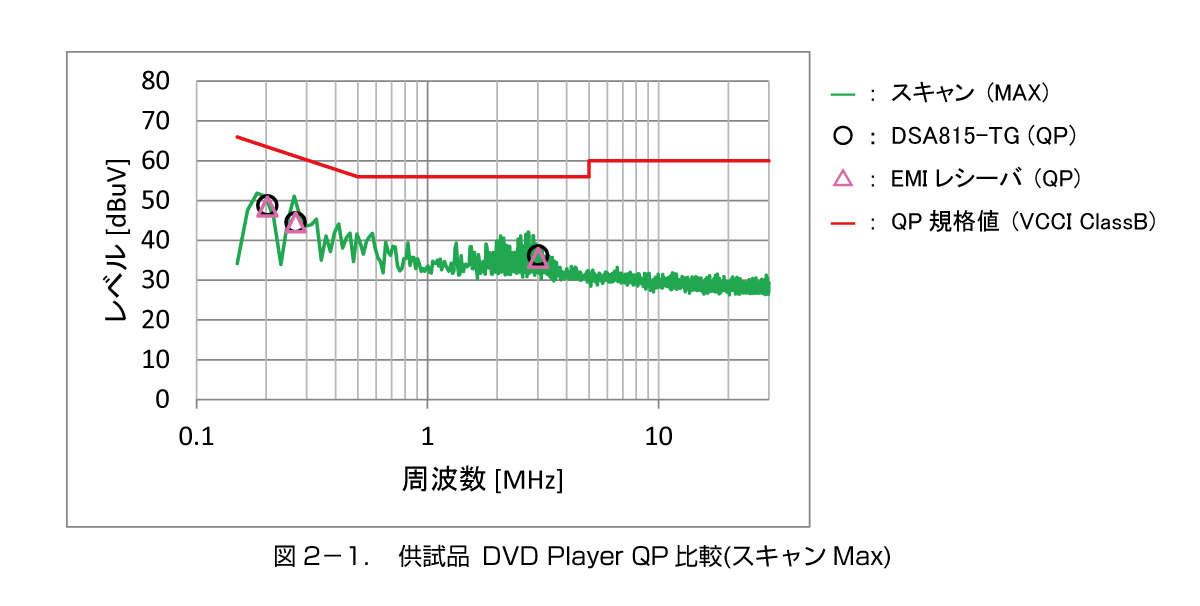

また、伝導エミッション測定評価も同様に1Ω/150Ω法にて評価を行い、変更する半導体製品(IC)の等価性の証明ができれば、製品性能は同等と見なすことができます。

現在、一部業界や業種では半導体EMC性能等価性評価を行い、EMC試験の工数削減への取り組みが始まりました。

【 製品開発プロセスに半導体EMC試験を組み込み工数削減 】

製品は企画→開発設計→基板設計→実装→組立のプロセスを経て作られます。完成後、EMC試験を行い、合格後に量産化へと進みますが、EMC試験でNGが出た場合、ノイズ対策を実施し設計のフェーズに戻るため工数が発生します。製品開発プロセスに半導体EMC試験をフロントローディングとして組み込むことにより、誤動作の主要因となりうる半導体製品(IC)を定量的に評価することができ、EMC対策の工数削減が見込めます。