規格情報 ISO 16750-2 Ed.4 2012( 電源電圧変動試験(DC))の概要

NoiseKen【 ISO 16750-2 Ed.4 2012の試験概要 】

1.一般的事項

この規格は、車両搭載機器に対する電気的負荷の電圧変動イミュニティについて記載しています。(EMCは除外)

電気的負荷は、車両のワイヤーハーネスや結線システムの電気抵抗により変動することがあります。

2.試験目的と方法および要求レベル

① 直流電源電圧

《目的》最小および最大電圧時の影響を確認

《試験》供試品(DUT)を駆動させるための全ての入力部に印加します。なお、関連する端子においては全ての電圧を測定する必要があります。

《試験レベル》

| 12V系製品 | 電源電圧(V) | |

| 最小Us | 最大Us | |

| A | 6 | 16 |

| B | 8 | |

| C | 9 | |

| D | 10.5 | |

| 24V系製品 | 電源電圧(V) | |

| 最小Us | 最大Us | |

| E | 10 | 32 |

| F | 16 | |

| G | 22 | |

| H | 18 | |

《要求》供試品(DUT)の各機能はISO16750-1記載のクラスAであること

② 過電圧

②-1 12Vシステム

②-1-1 Tmax-20℃の温度での試験

《目的》レギュレータ故障時に出力電圧が過電圧になった際の影響を確認

《試験》DUTを、最高動作温度を20℃下回る温度に加熱し、全ての入力部に18Vの電圧を60分印加します。

《要求》DUTの各機能はISO16750-1記載のクラスCであること。(より厳しい要求事項が必要な場合はクラスA)

②-1-2 室温での試験

《目的》ジャンプスタート時の影響を確認

《試験》DUT室温で安定している状態で、全ての入力部に24Vの電圧を60±6秒印加します。

《要求》 DUTの各機能はISO16750-1記載のクラスD以上であること。(より厳しい要求事項が必要な場合はクラスB)

②-2 24Vシステム

②-2-1 Tmax-20℃の温度での試験

《目的》レギュレータ故障時に出力電圧が過電圧になった際の影響を確認

《試験》DUTが最高動作温度を20℃下回る温度に加熱し、全ての入力部に36Vの電圧を60分印加します。

《要求》DUTの各機能はISO16750-1記載のクラスCであること。(より厳しい要求事項が必要な場合はクラスA)

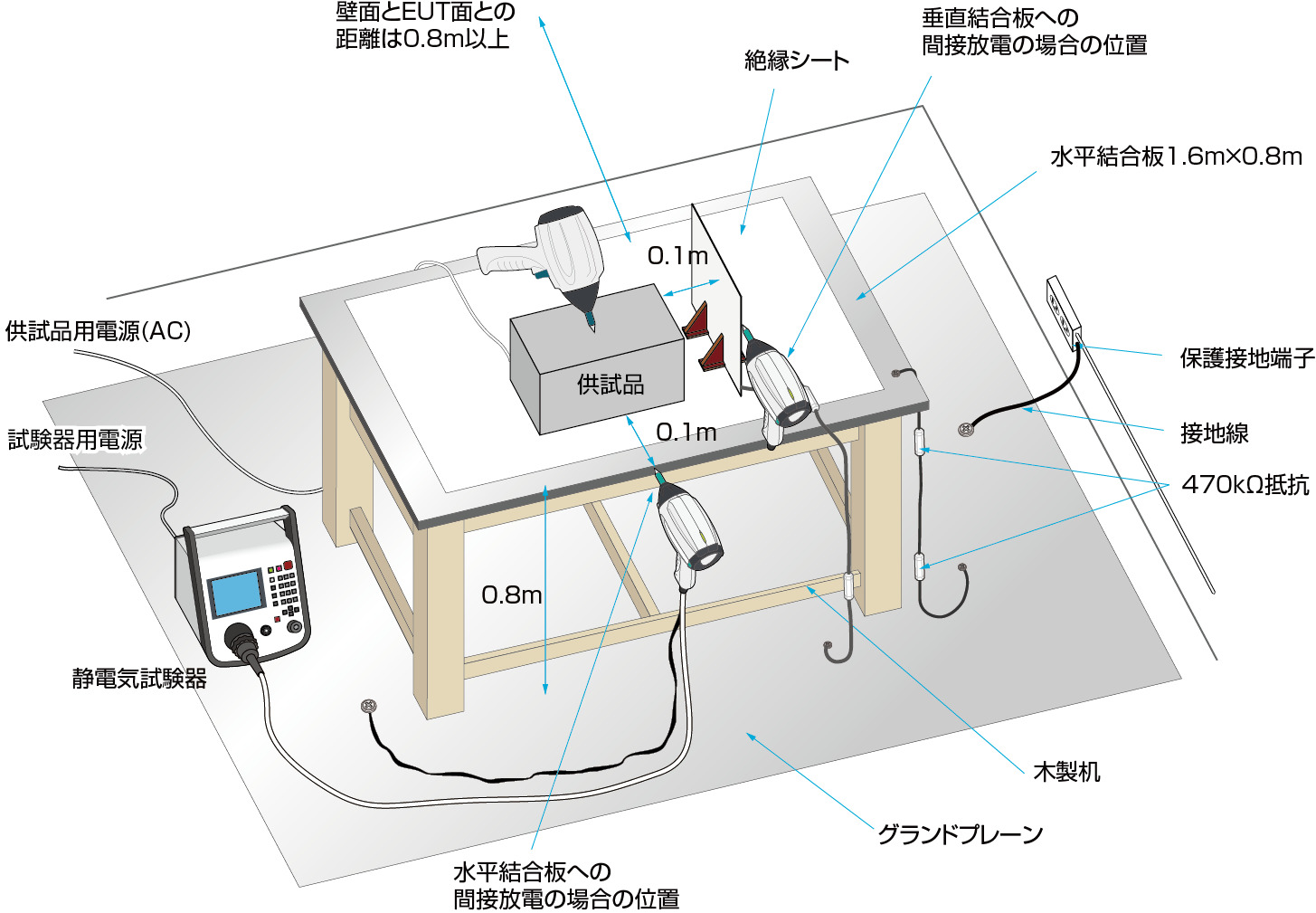

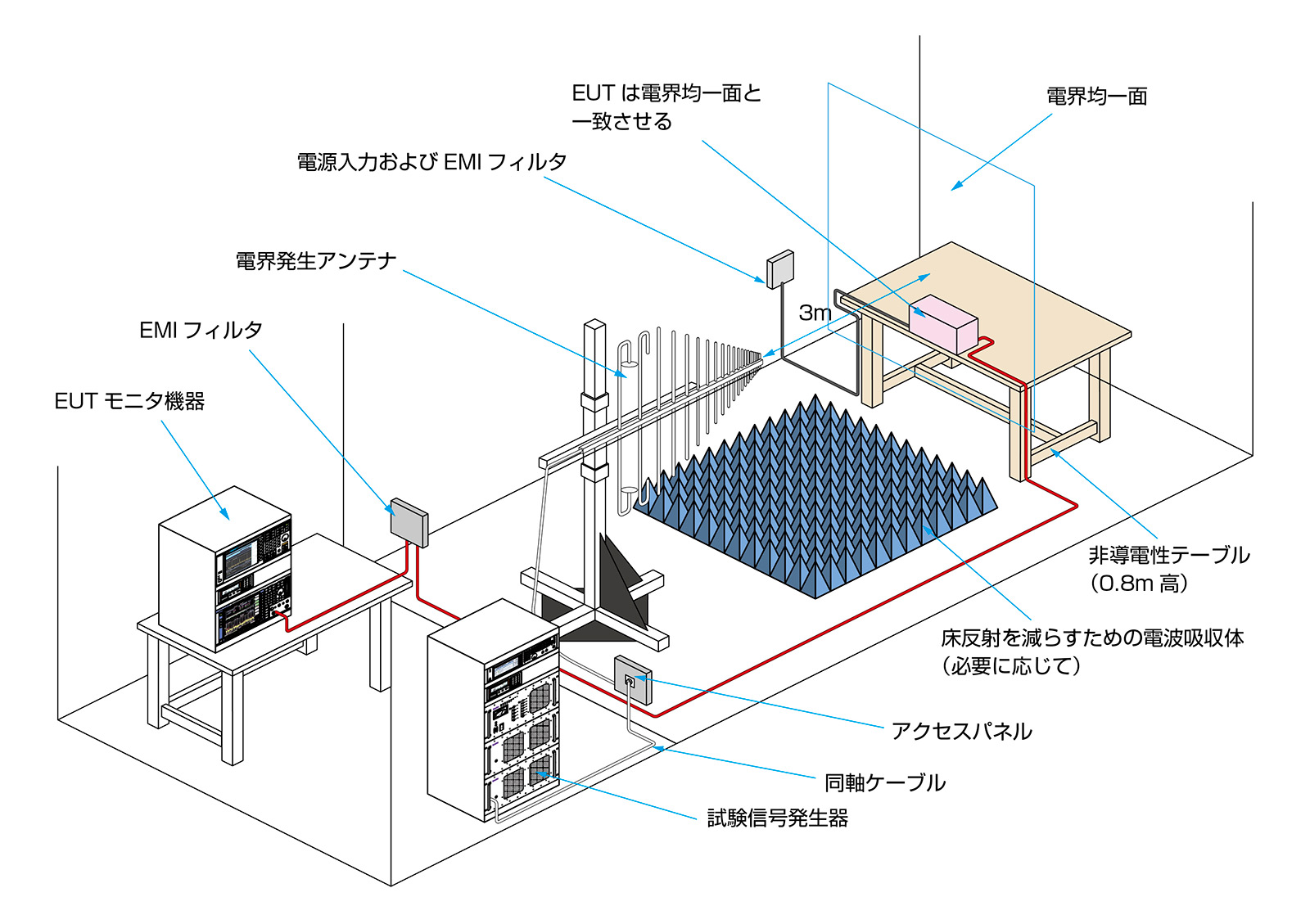

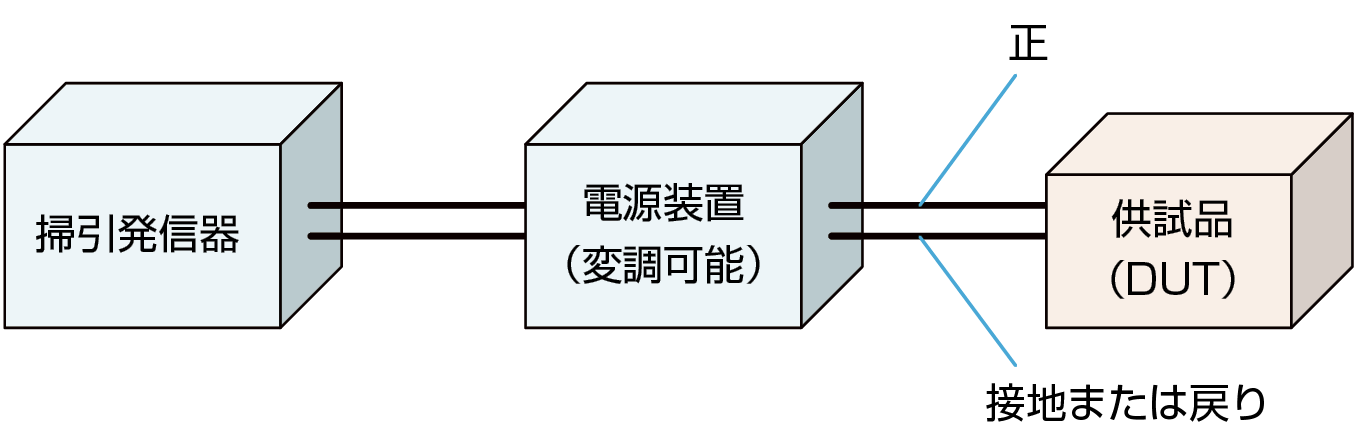

③ 重畳交流電圧

《目的》直流電源の残留交流の影響を確認

《試験》DUTの、該当する全ての入力部に対して、下記の試験を実施します。

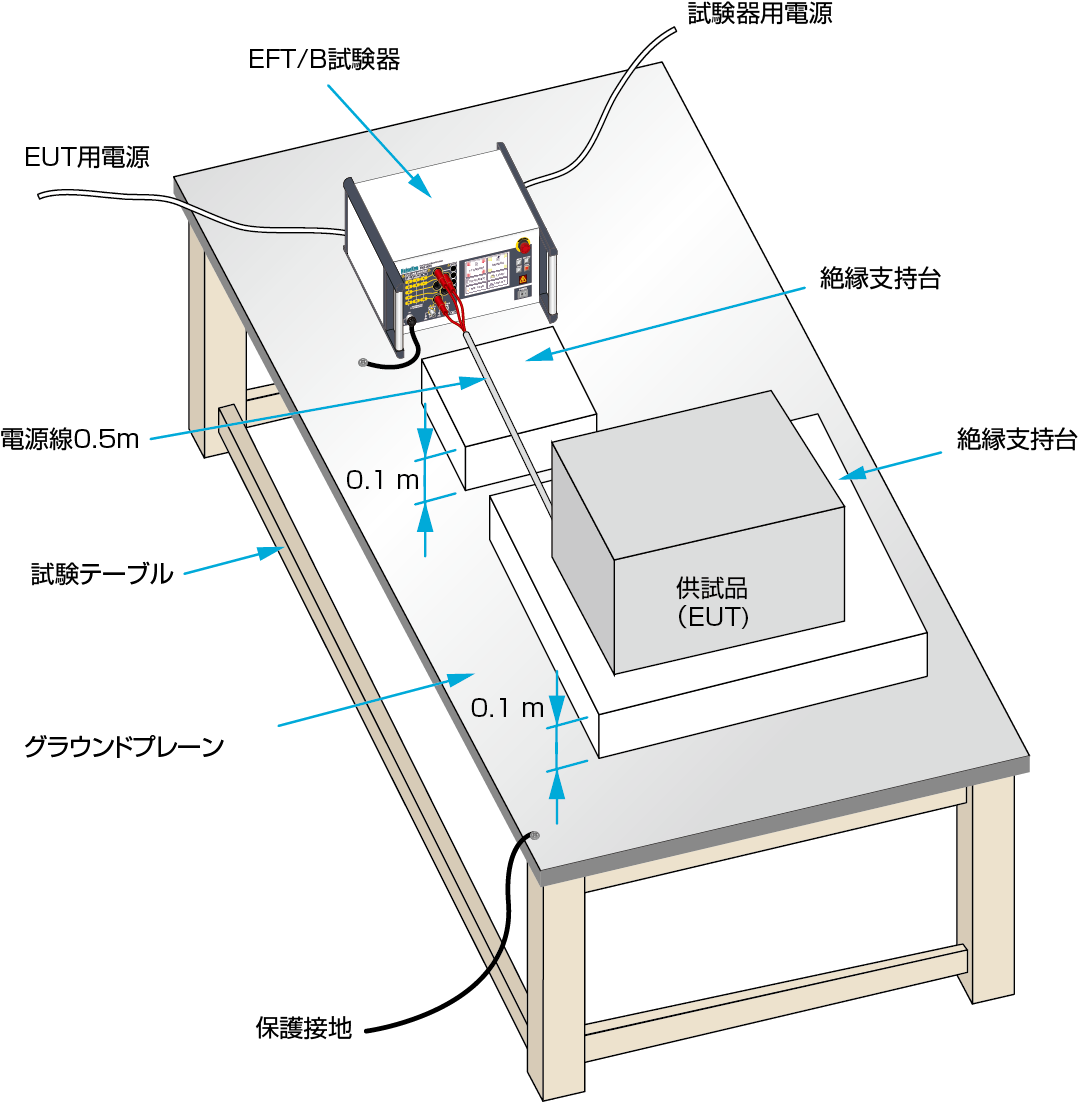

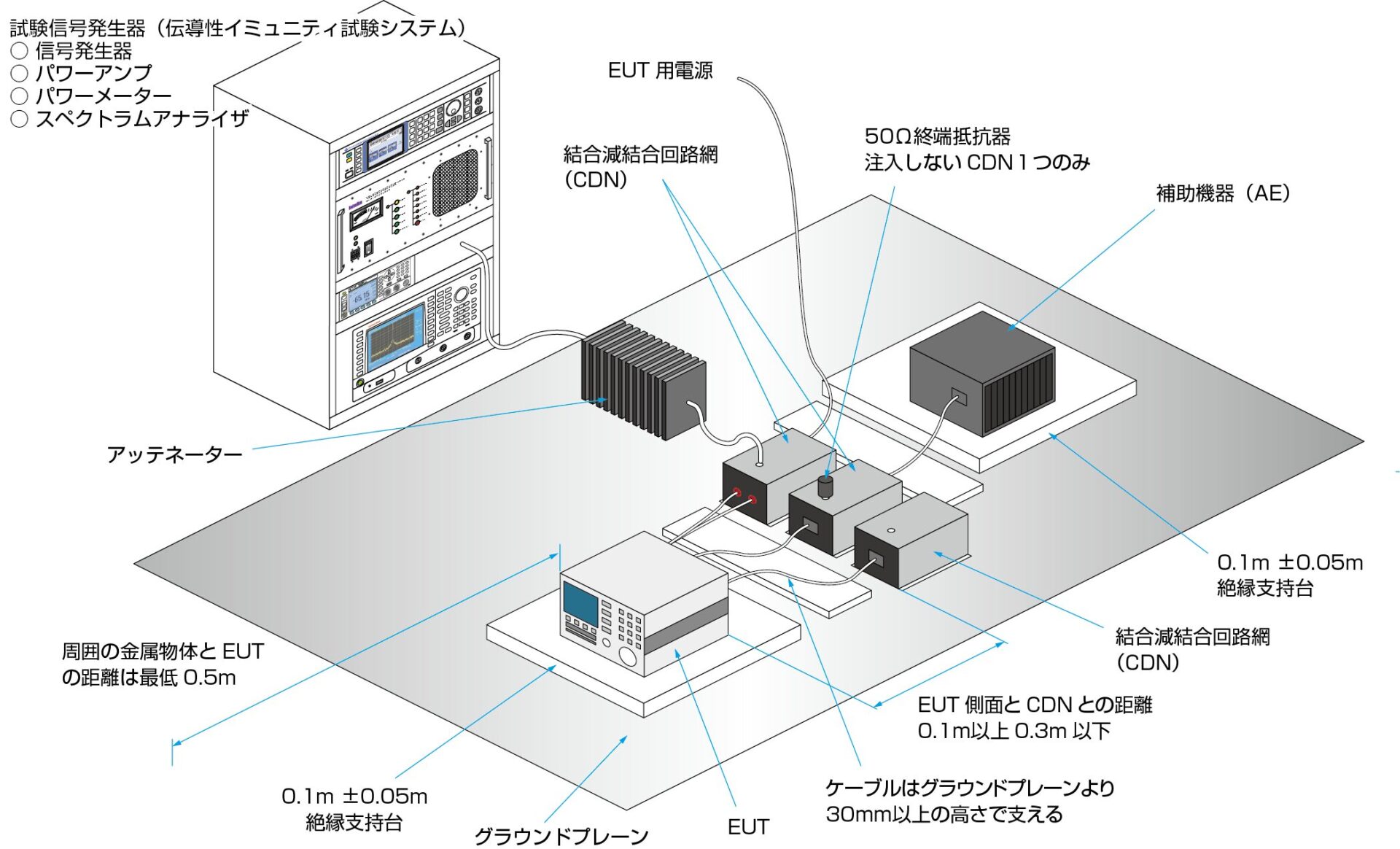

《試験配置》

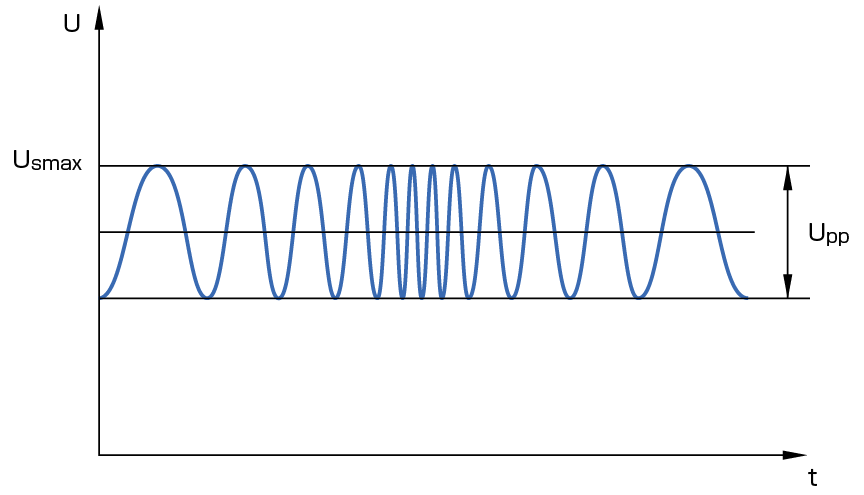

《試験レベル》

| 12V系 | 24V系 | ||

| 試験電圧Us max (図1参照) | 16V | 32V | |

| 交流電圧(正弦) Upp | 厳しさレベル1 | 1V | |

| 厳しさレベル2 | 4V | ||

| 厳しさレベル3 | - | 10V | |

| 厳しさレベル4 | 2V | - | |

| 電源内部の抵抗 | 50~100mΩ | ||

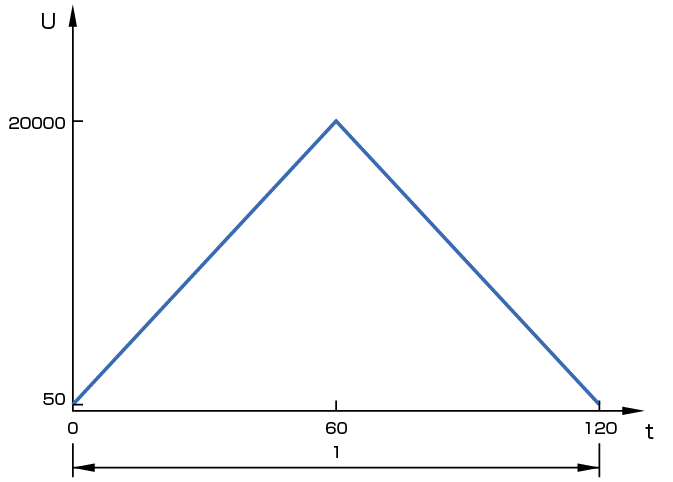

| 周波数範囲 (図2参照) | 50Hz~25kHz | ||

| 周波数掃引タイプ (図2参照) | 三角・対数 | ||

| 掃引時間 | 120秒 | ||

| 掃引回数 | 5回(連続) | ||

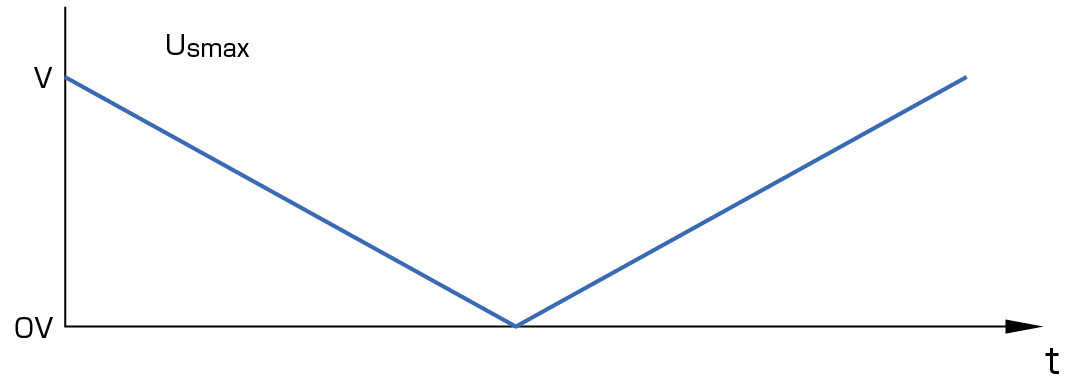

正弦波交流電圧を重畳させた試験電圧

周波数掃引

《要求》DUTの各機能はISO16750-1記載のクラスAであること

④ 電源電圧の緩速増減

《目的》バッテリの緩やかな放電及び再充電時の影響を確認

《試験》DUTの該当する全ての入力部に対して下記の試験を実施します。電源電圧Usminから0Vへ減少し、その後0VからUsminまで上昇させます。変化のスピードは、0.5V (±0.1V)/分とするか、又は25mV以下の等ステップです。

《要求》DUTの各機能はISO16750-1記載のクラスDであること(より厳しい要求事項が必要な場合はクラスC)

⑤電源電圧の不連続性

⑤-1 瞬時低下

《目的》ヒューズが別回路内で溶融した際の影響を確認

《試験》DUTの該当する全ての入力部に対して下記の試験を同時に印加します。立上り/立下り時間は10ms以下です。

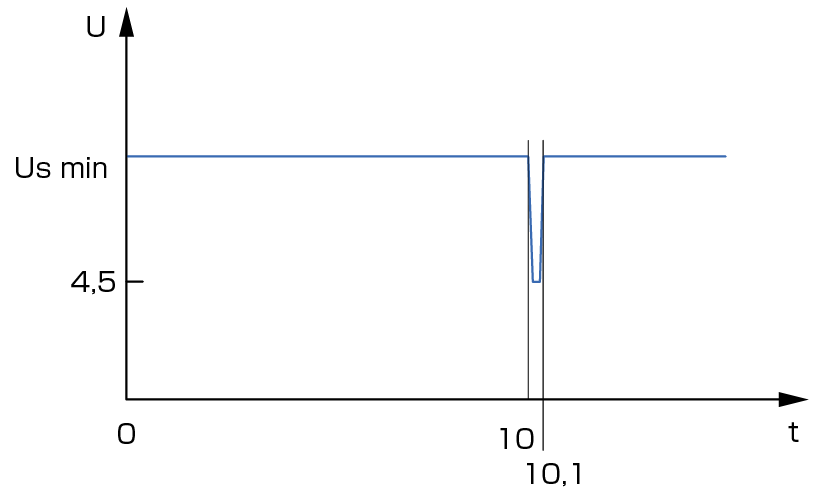

12V系

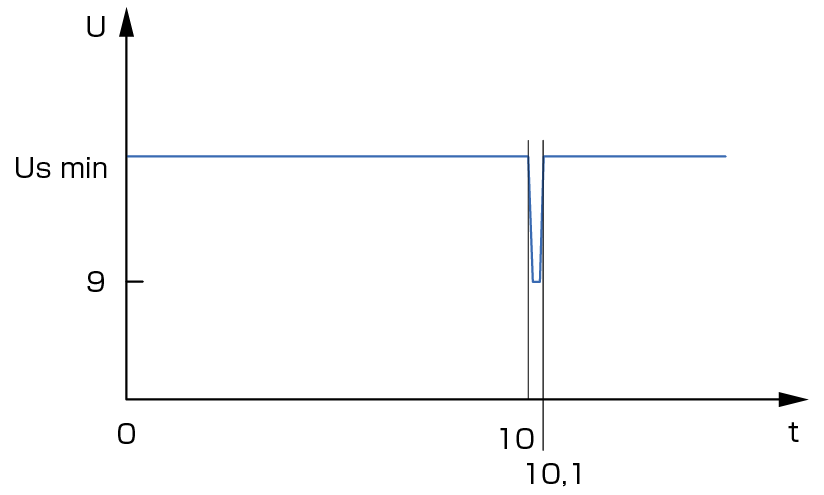

24V系

《要求》DUTの各機能はISO16750-1記載のクラスBであること。仕向け先との合意によりリセットしてもよい。

⑤-2 リセット挙動

《目的》電圧低下時のリセット挙動によるDUTの影響を確認

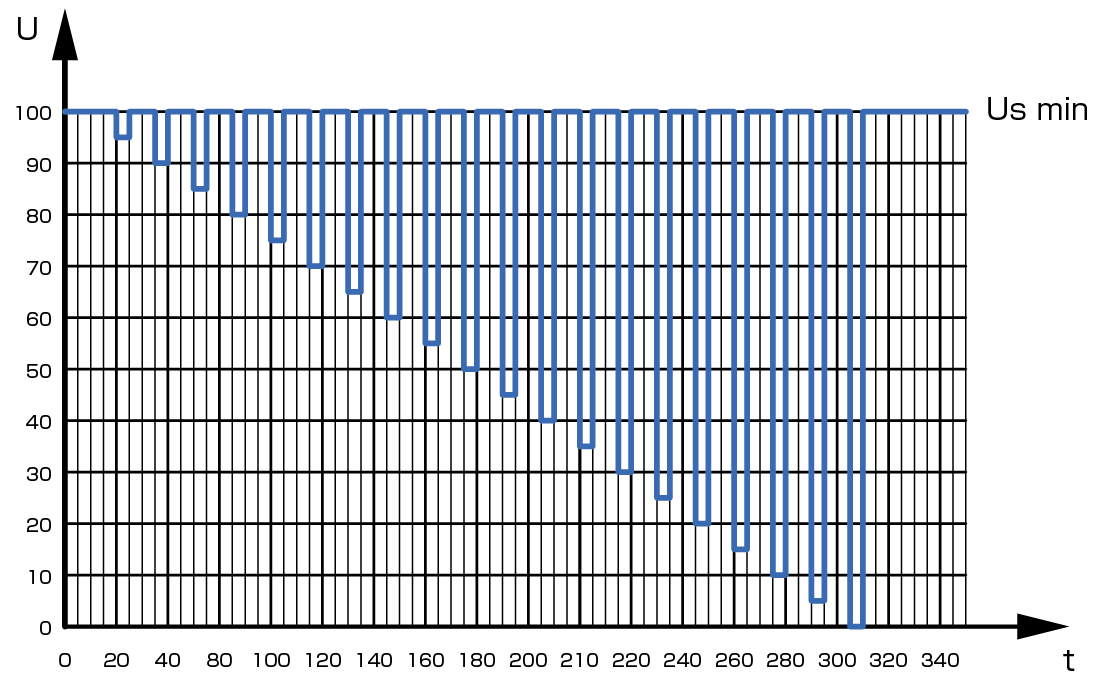

《試験》DUTの該当する全ての入力部に対して下記の試験を実施する。電源電圧を、最低電源電圧Usminから0.95Usminまで5%ずつ引き下げる。この電圧を5秒間維持した後にUsminまで引き上げ10秒以上維持する。次に0.9Usminまで引き下げ、この電圧を5秒間維持た後にUsminまで引き上げる。これらを下図のように下方値が0VになるまでUsminを5%ずつ段階的に引き下げた後に再度、Usminま引き上げる。

《要求》DUTの各機能はISO16750-1記載のクラスCであること

⑤-3 起動プロフィール

《目的》クランキング中およびその後のDUTの影響を確認

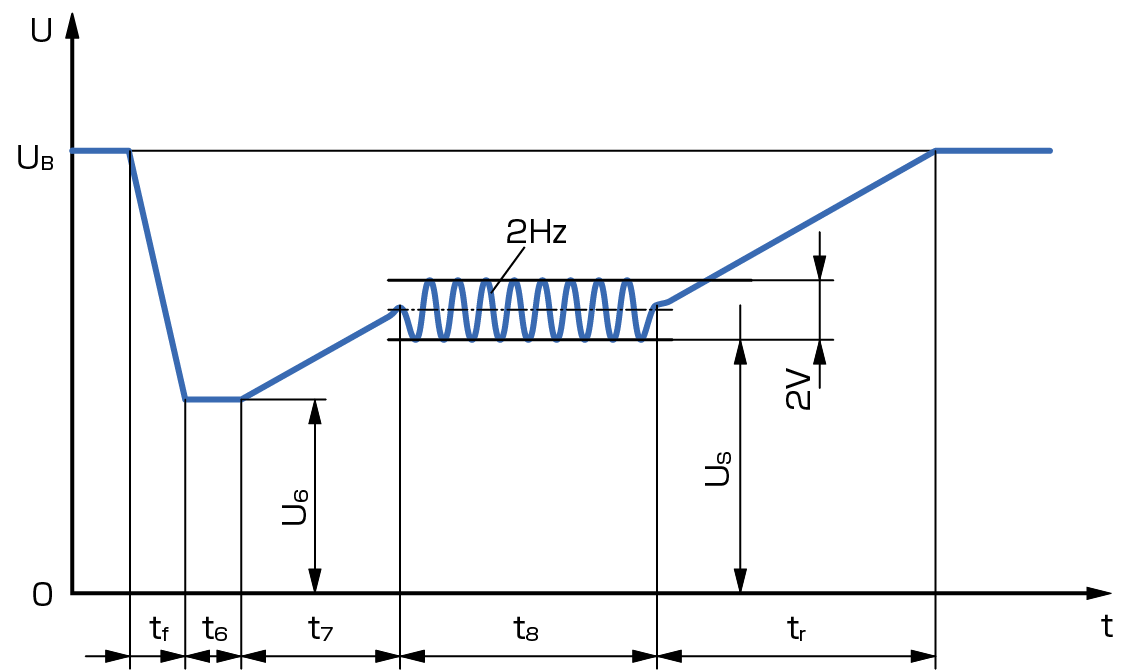

《試験》DUTの、該当する全ての入力部に対して、下記の図および表の試験を実施します。起動サイクルとサイクルの間の休止時間は1~2秒を推奨しています。

公称電圧が12Vのシステムの起動プロフィールの値(UN)

| パラメタ | レベル | ||||

| I | II | III | IV | ||

| 電圧 V | Us6 | 8(-0.2) | 4.5(-0.2) | 3(-0.2) | 6(-0.2) |

| Us | 9.5(-0.2) | 6.5(-0.2) | 5(-0.2) | 6.5(-0.2) | |

| 接続時間 ms | tf | 5(±0.5) | 5(±0.5) | 5(±0.5) | 5(±0.5) |

| t6 | 15(±1.5) | 15(±1.5) | 15(±1.5) | 15(±1.5) | |

| t7 | 50(±5) | 50(±5) | 50(±5) | 50(±5) | |

| t8 | 1000(±100) | 10000(±1000) | 1000(±100) | 10000(±1000) | |

| tr | 40(±4) | 100(±10) | 100(±10) | 100(±10) | |

| 最低の機能状態 | Aa | Ba | Ba | Aa | |

| Ab | Bb | Cb | Bb | ||

| Bc | Cc | Cc | Cc | ||

| Bd | Cd | Cd | Cd | ||

| a Us min = 6V; Us max = 16V b Us min = 8V; Us max = 16V c Us min = 9V; Us max = 16V d Us min = 10.5V; Us max = 16V | |||||

公称電圧が24Vのシステムの値(UN)

| パラメタ | レベル | |||

| I | II | III | ||

| 電圧 V | Us6 | 10(-0.2) | 8(-0.2) | 6(-0.2) |

| Us | 20(-0.2) | 15(-0.2) | 10(-0.2) | |

| 接続時間 ms | tf | 10(±1) | 10(±1) | 10(±1) |

| t6 | 50(±5) | 50(±5) | 50(±5) | |

| t7 | 50(±5) | 50(±5) | 50(±5) | |

| t8 | 1000(±100) | 10000(±1000) | 1000(±100) | |

| tr | 40(±4) | 100(±10) | 40(±10) | |

| 最低の機能状態 | Aa | Ba | Ba | |

| Ab | Bb | Cb | ||

| Bc | Cc | Cc | ||

| Bd | Cd | Cd | ||

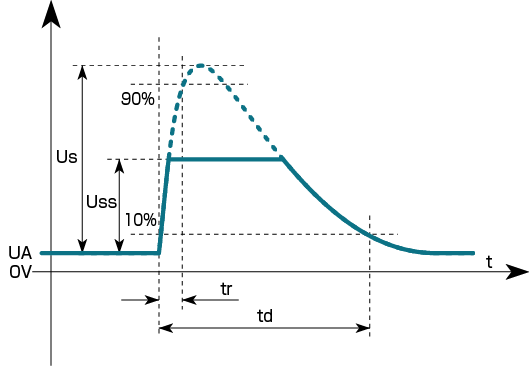

t 時間

U 試験電圧

tf 立ち下がり勾配

tr 立ち下がり勾配

t6,t7,t8 持続パラメータ(前項表参照)

UB 作動中でないジェネレータ電源

US 電源電圧

US6 t6における電源電圧

《要求》クランキング中の車両機能に関係する機器はクラスA、その他は前項表に従います。

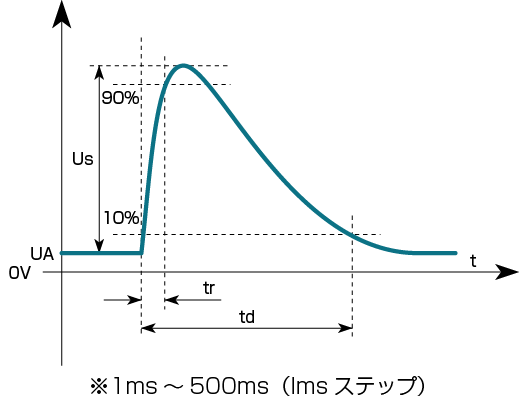

⑤-4 負荷遮断(ロードダンプ)

《目的》オルタネータ回路上に残留しているその他の負荷を伴ってオルタネータが充電電流を生成した時、放電バッテリの接続が遮断される場合に発生するロードダンプ過渡による影響を確認

《試験》試験パルスジェネレータは、集中ロードダンプ抑制を伴わない試験と伴う試験に従ったロードダンプ試験パルスを生成する能力がなければなりません。

集中ロードダンプ抑制を伴わない試験Aのパルス

| パラメタ | システムのタイプ | 最低限の 試験要求事項 | |

| UN=12V | UN=24V | ||

| Usa | 79~101V | 151~202V | 1分間隔で 10パルス |

| Ria | 0.5~4Ω | 1~8Ω | |

| td | 40~400ms | 100~350ms | |

| tr | 10ms +0/-5ms | ||

| a特に合意のない限り、内部抵抗の高い値には高い電圧レベルを使用するか、又は内部抵抗の低い値には低い電圧レベルを使用する。 | |||

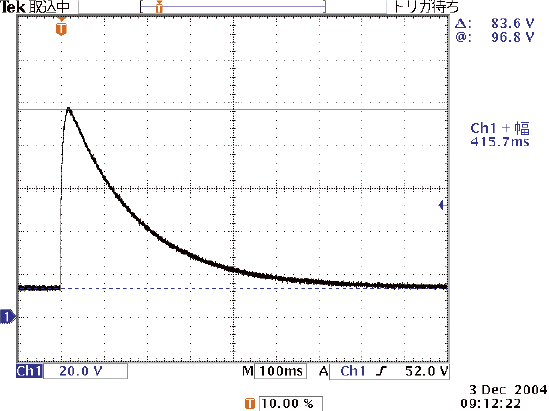

出力波形

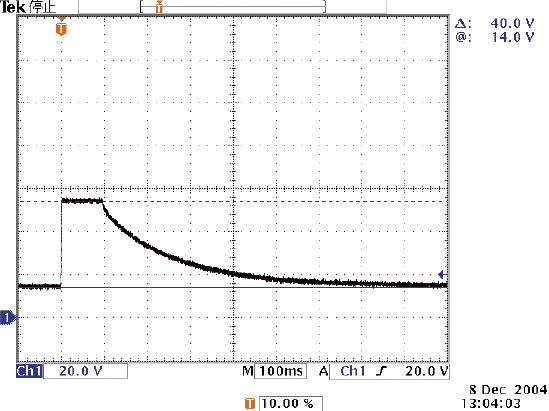

実際の波形

集中ロードダンプ抑制を伴う試験Bのパルス

| パラメタ | システムのタイプ | 最低限の 試験要求事項 | |

| UN=12V | UN=24V | ||

| Usa | 79~101V | 151~202V | 1分間隔で 5パルス |

| Us* | 35 | 顧客の指定による (一般値は58) | |

| Ria | 0.5~4Ω | 1~8Ω | |

| td | 40~400ms | 100~350ms | |

| t3 | 10ms +0/-5ms | ||

| a特に合意のない限り、内部抵抗の高い値には高い電圧レベルを使用するか、又は内部抵抗の低い値には低い電圧レベルを使用する。 | |||

出力波形

実際の波形

《要求》機能状態は、ISO 16750-1に定義するとおり最低限クラスCであること。

⑥ 逆電圧

《目的》補助起動装置使用時のバッテリ逆接続による影響を確認

※適用除外・・・ジェネレータ、外部逆極性保護装置のないクランピングダイオードつきリレー

《試験》実車と同様にDUTと接続し、ヒューズをつけます。極性を逆転させた電源端子に下記のケースから選択した試験電圧を同時に印加します。

・ケース1 オルタネータ回路にヒューズがない車両かつ整流器ダイオードが逆電圧に60秒耐えられる車両でDUTを使用する場合、DUTの入力端子部に対して逆性を接続し、4Vの試験電圧を60秒±10%同時に印加します。 (24V系は適用外)

・ケース2 DUTの入力端子部に対して逆性を接続し、12V系は14V、24V計は28Vの試験電圧を60秒±10%同時に印加します。

試験電圧

| 公称電圧、UN | 試験電圧、UA |

| 12V | 14V |

| 24V | 28V |

《要求》溶断したすべてのヒューズを交換した後、DUTの各機能はISO16750-1記載のクラスAであること

⑦ 基準グラウンド及び電源オフセット

《目的》2つ以上の電源バスを有する場合のコンポーネント評価

《試験》車両構成を模擬するために、全ての入出力部を代表的な負荷または回路網に接続し、Uaを印加して通常動作を確認します。(オフセット電圧は1.0V)

《要求》すべての機能グループにおいてDUTの各機能はクラスA:動作不良またはラッチアップがあってはいけません。

⑧ 開路試験

⑧-1 単線遮断

《目的》開接点条件の影響を確認(※コネクタに関する試験ではありません。)

《試験》DUTを意図されたように接続し、システムの回路を一つOPENにし、さらに接続しなおします。OPEN状態と再接続状態でのDUTの動作を確認します。遮断時間-10秒 ±10% 開路抵抗≧10MΩ

《要求》DUTの各機能はISO16750-1記載のクラスCであること

⑧-2 複線遮断

《目的》DUTを急速に複線遮断した際の影響を確認(※コネクタに関する試験ではありません。)

《試験》DUTを切り離し、再度、接続しなおします。切断状態と再接続状態でのDUTの動作を確認します。遮断時間-10秒 ±10% 開路抵抗≧10MΩ

《要求》DUTの各機能はISO16750-1記載のクラスCであること

その他の試験としては、以下があります。

⑨ 短絡保護

⑨-1 信号回路

《目的》装置の入出力部での短絡時の影響を確認

⑨-2 負荷回路 《目的》装置の入出力部での短絡時の影響を確認

⑩ 耐電圧

《目的》電気的に絶縁された回路において電圧の影響を確認

⑪ 絶縁抵抗

《目的》電気的に絶縁された誘導負荷をもつ回路が発生する電圧に対する耐電圧を確認する。

注意: この試験概要は、ISO16750-2 Ed.4 2012規格を元に記載しております。詳細な試験方法等や試験のクラス分類につきましては規格書の原文をご確認ください。